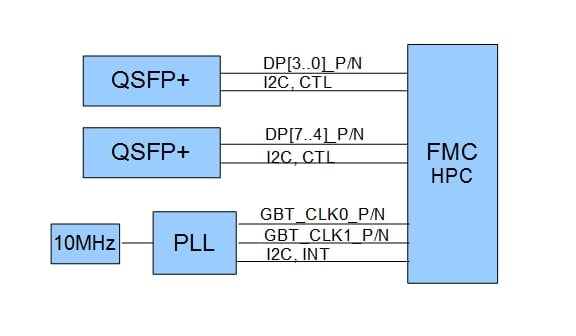

The QSFP ports are compatible with SFF-8436 transceivers, supporting both copper and fiber optic links. The two ports are fully independent on the module. QSFP control and monitoring signals are mapped to the FMC interface for I2C control port, power mode, reset, presence of cable, and Interrupt events.

A flexible reference clock for on the FMC-QSFP is fully programmable over the 0.16 to 350 MHz range. The clock can be programmed for all common rates for standards such as OC-12, OBSAI, CPRI, GbE, sFPDP and SONET. The clock has jitter performance of less than 1 ps RMS max, allowing it to meet the most stringent requirements for these applications. An on-card 10MHz Oscillator with 0.5 PPM stability is used as the PLL reference.

The FMC-QSFP is fully electrically compatible with FMC (ANSI/VITA 57) specifications for IO module. Mechanically, the module will fit FMC sites, however the QSFP connectors protrude slightly past the face of the bezel. The module is compatible with FMC HPC sites. The module consumes <750 mW exclusive of QSFP modules.

The FMC is provided with VHDL code illustrating the interfaces. Specific FPGA and platform support is provided for Innovative’s VPXCOP and PEX-COP FPGA cards.

Software libraries and examples for C host development are provided. Application examples demonstrating the module features are provided for Innovative Integration platforms in for Windows, Linux and VxWorks.